Product Summary

The CY62256 is a high-performance CMOS static RAM organized as 32K words by 8 bits. Easy memory expansion is provided by an active LOW chip enable (CE) and active LOW output enable (OE) and Tri-state drivers. This device has an automatic power-down feature, reducing the power consumption by 99.9% when deselected. An active LOW write enable signal (WE) controls the writing/reading operation of the memory. When CE and WE inputs are both LOW, data on the eight data input/output pins (I/O0 through I/O7) is written into the memory location addressed by the address present on the address pins (A0 through A14). Reading the device is accomplished by selecting the device and enabling the outputs, CE and OE active LOW, while WE remains inactive or HIGH. Under these conditions, the contents of the location addressed by the information on address pins are present on the eight data input/output pins. The input/output pins remain in a high-impedance state unless the chip is selected, outputs are enabled, and write enable (WE) is HIGH

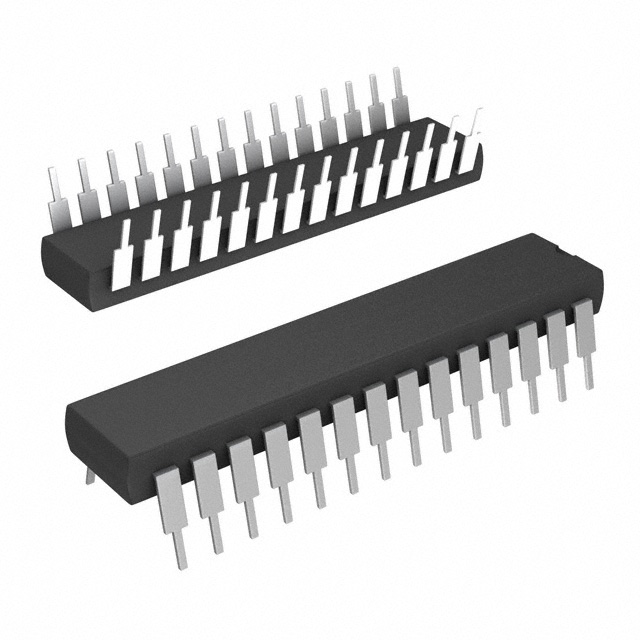

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|---|---|---|---|---|---|---|---|---|---|---|

|

CY62256LL-70PXC |

|

IC SRAM 256KBIT 70NS 28DIP |

Data Sheet |

Negotiable |

|

||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||

|

CY62126BV |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CY62126DV30 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

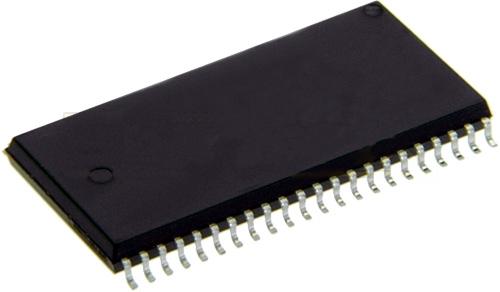

CY62126DV30L-55BVXE |

Cypress Semiconductor |

SRAM SLO 3.0V SUPER LO PWR 64K X 16 SRAM |

Data Sheet |

Negotiable |

|

||||

|

CY62126DV30L-55BVXET |

Cypress Semiconductor |

SRAM SLO 3.0V SUPER LO PWR 64K X 16 SRAM |

Data Sheet |

Negotiable |

|

||||

|

CY62126DV30L-55ZSXE |

Cypress Semiconductor |

SRAM SLO 3.0V SUPER LO PWR 64K X 16 SRAM |

Data Sheet |

Negotiable |

|

||||

|

CY62126DV30L-55ZSXET |

Cypress Semiconductor |

SRAM SLO 3.0V SUPER LO PWR 64K X 16 SRAM |

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)